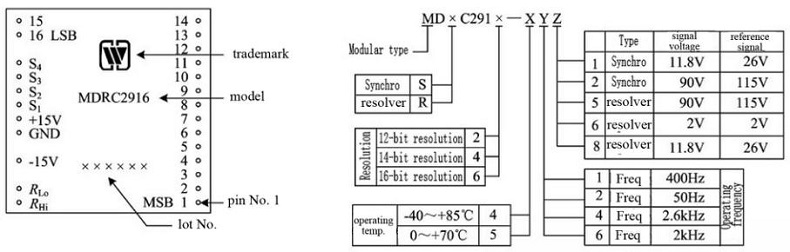

1.Características (consulte la Fig. 1 para ver la vista exterior y la Tabla 1 para ver los modelos)

| Compatible con nivel DTL/TTL/CMOS |  |

| Resolución de 12 bits, 14 bits y 16 bits | |

| Protección contra cortocircuito y sobrecarga | |

| Caja de metal, con buen rechazo de calor. | |

| Potencia de salida: 5W |

Tabla1 Modelos de productos

12 bits | 14 bits | 16 bits | |||

sincronizado | resolver | sincronizado | resolver | sincronizado | resolver |

MDSC2912-411 | MDRC2912-418 | MDSC2914-411 | MDRC2914-418 | MDSC2916-411 | MDRC2916-418 |

MDSC2912-412 | MDRC2912-438 | MDSC2914-412 | MDRC2914-438 | MDSC2916-412 | MDRC2916-438 |

MDSC2912-421 | MDRC2912-414 | MDSC2914-421 | MDRC2914-414 | MDRC2916-414 | |

MDSC2912-422 | MDRC2912-415 | MDSC2914-422 | MDRC2914-415 | MDRC2916-41-36/11.8 | |

MDRC2916-415 | |||||

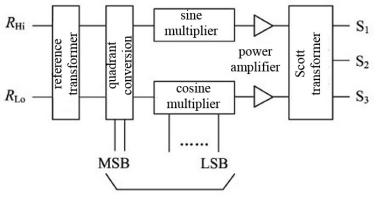

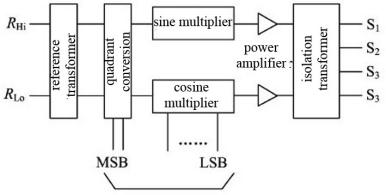

y emite una señal de sincronización/resolución de alta precisión después de la conversión. Él | El producto está equipado con un circuito de amplificación de potencia en su interior, y su La potencia de salida puede alcanzar los 5W. 4. Rendimiento eléctrico |

(Tabla 2 y Tabla 3) de la serie MDSC/MDRC29 | Convertidores de digital a sincronizado o convertidores de digital a resolver Tabla 2 Condiciones nominales y condiciones de funcionamiento recomendadas máx. valor absoluto de calificación Tensión de alimentación +VS: +13,5~+17,5V Tensión de alimentación -VS: -17,5~-13,5 V Rango de temperatura de almacenamiento: -40~100℃ |

Tensión de alimentación -VS: -16,5~-14,25 V | Voltaje de referencia (valor efectivo) VRef*: 115V±5% | Tensión de señal (valor efectivo) V1*: 90V±5% | Frecuencia de referencia f*: 400Hz±10% | Rango de temperatura de funcionamiento TA: -40 ℃ ~ 85 ℃ | |||

Nota: * indica que se puede personalizar según los requisitos del usuario.| | |||||||

Tabla 3 Características eléctricas | Parámetro | MDRC/DSC2912 | MDRC/DSC2914 | MDRC/DSC2916 | |||

Unidad | ±8 | ±4 | ±4 | Estándar militar empresarial (Q/HW30857-2006) | |||

Resolución | 5 | 0 | 5 | 0 | 5 | 0 | V |

12 bits | 14 bits | V | |||||

16 bits | Poco | Hz | |||||

Exactitud Minuto | Entrada digital Tensión de referencia (valor efectivo) | V | |||||

26, 36, 115V±10%﹡ | 5 | W | |||||

|  |

| (línea-línea, resolver o sincro)﹡ | Potencia de salida |

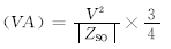

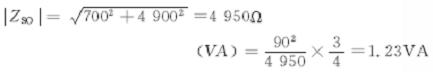

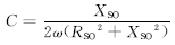

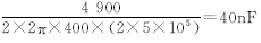

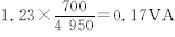

La potencia requerida es: (VA) (sin ajustar) xEn el ejemplo anterior, la capacitancia es:La potencia requerida después del ajuste es: | En el diseño se requiere anotar los errores que suelen existir como número de bobina, capacitancia, inductancia, etc. en los TC.Indicaciones prácticas para el ajuste de la carga del TC:① No se requiere capacitancia de alta precisión, un error del 20% es suficiente. |

|  |

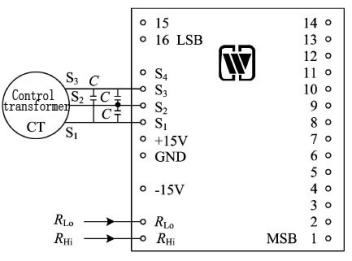

| ② Se deben usar tres condensadores entre S1 y S2, S2 y S3, así como entre S3 y S1. ③ Tensión soportada y tipo de capacitancia | Para un voltaje de línea a línea de 11,8 V, el voltaje de resistencia de la capacitancia |

capacidad. | Para un voltaje de línea a línea de 90 V, el voltaje de resistencia de la capacitancia | entre pines es 150VAC, y se permite usar capacitancia cerámica | con baja constante dieléctrica. | ④ El ajuste de carga del resolver solo requiere dos capacitancias. Uno es | conectado entre S1 y S3, y el otro entre S2 y S4. | (2) Transductor diferencial de control (CDX) | La carga de DSC en el equipo se puede considerar como carga de CT, pero su | La impedancia equivalente Z debe calcularse como la carga del TC, su valor es |

1 | generalmente 66%~80% de ZSO. | (3) Receptor de par (TR) | 11 | 11 | En comparación con CT y CDX, es relativamente difícil controlar el | 21 | S1 | receptor de par (TR). En términos generales, requiere una salida |

2 | 2 | amplificador. Debido a que el vector de cambio de radio de la serie MDSC/MDRC28 | 12 | 12 | producto puede ser despreciado, es más adecuado para controlar TR que | 22 | aquellos dispositivos con un error de ±7%. Para un error con el ángulo θ, el | excitante corriente es: |

3 | 3 | Indicaciones: | 13 | 13 | ①TR no debe bloquearse. | 23 | ②El avance correspondiente desde el extremo de entrada de referencia hasta DSC se ajustará a las disposiciones de TR. | ③La entrada de referencia debe aplicarse siempre en TR y convertidor. |

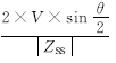

4 | 4 | El voltaje de salida de DSC/DRC debe coincidir completamente con el voltaje requerido por TR. | 14 | 14 | 7. Curva MTBF | 24 | NC | (Fig. 5) de la serie MDSC/MDRC29 |

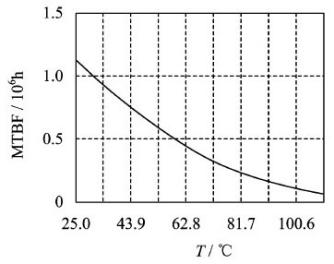

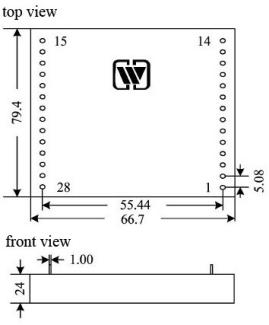

5 | 5 | Convertidores de digital a sincronizado o convertidores de digital a resolver | 15 | 15 | 8. Designación de clavijas (Fig. 6, Tabla 4) de la serie MDSC/MDRC29 | 25 | Convertidores de digital a sincronizado o convertidores de digital a resolver | Fig.5 Curva MTBF-temperatura |

6 | 6 | (Nota: según GJB/Z299B-98, buen estado del terreno previsto) | 16 | 16 | Fig.6 Diagrama esquemático de pines (vista superior) Tabla 4 Designación de pines | 26 | NC | Clavo |

7 | 7 | Símbolo | 17 | NC | Función | 27 | Clavo | Símbolo |

8 | 8 | Función | 18 | S4 | Clavo | 28 | Símbolo | Función |

9 | 9 | 1 (MSB) | 19 | S3 | Entrada digital 1 | |||

10 | 10 | Entrada digital 11 | 20 | S2 | Salida de señal 1 |

Entrada digital 2

Entrada digital 12

+15V

entrada +15V

Entrada digital 3

Entrada digital 13

dejar desconectado | Entrada digital 5 | Entrada digital 15 | (12 bits y 14 bits se dejan desconectados) | -15V | -Entrada de 15V |

1 | Entrada digital 6 | 6 | Entrada digital 16 | 11 | (12 bits y 14 bits se dejan desconectados) |

2 | dejar desconectado | 7 | Entrada digital 7 | dejar desconectado | RLo |

3 | Extremo inferior de la entrada de referencia | 8 | Entrada digital 8 | 13 | Salida de señal 4 |

4 | RHola | 9 | Entrada de referencia de gama alta | Entrada digital 9 | Salida de señal 3 |

5 | Entrada digital 10 | 10 | Salida de señal 2 |

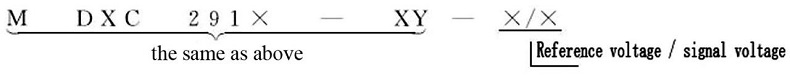

X

X