| Frecuencia de excitación 50 Hz, 400 Hz y 2,6 kHz |  |

| Resolución: 10 bits, 12 bits, 14 bits | |

| Alta velocidad de seguimiento | |

| La entrada no estándar es ajustable a través de una resistencia externa o se ajusta en el terminal de entrada del producto | |

| Salida de voltaje de CC directamente proporcional a la velocidad angular | |

| Compatible con la serie SDC1700 de American AD company |

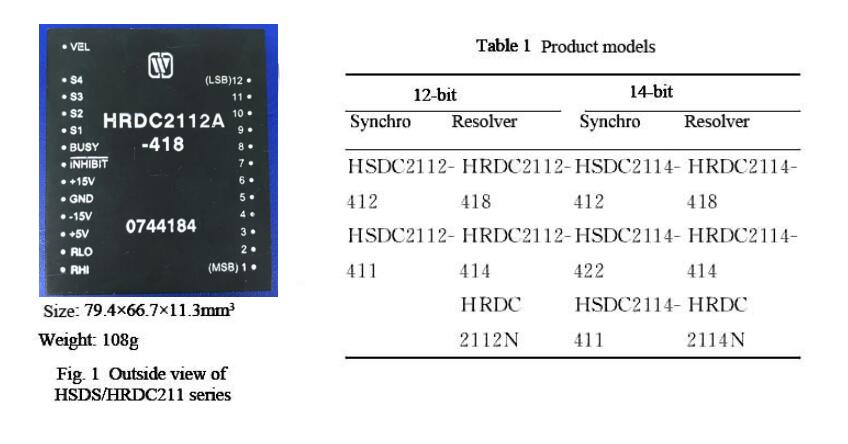

conversión. | La potencia de funcionamiento es de ±15V y +5V DC de potencia. Hay dos tipos de |

señal de salida: sincronización de tres líneas y señal de referencia (convertidor SDC) | |

o resolución de cuatro líneas y señal de referencia (convertidor RDC); La salida | |

es códigos digitales paralelos del sistema binario. | 4 Rendimiento eléctrico (Tabla 2, Tabla 3) de Synchro a |

Convertidores digitales o Resolver to Digital Converters (HSDC/HRDC211 | |

Serie) | |

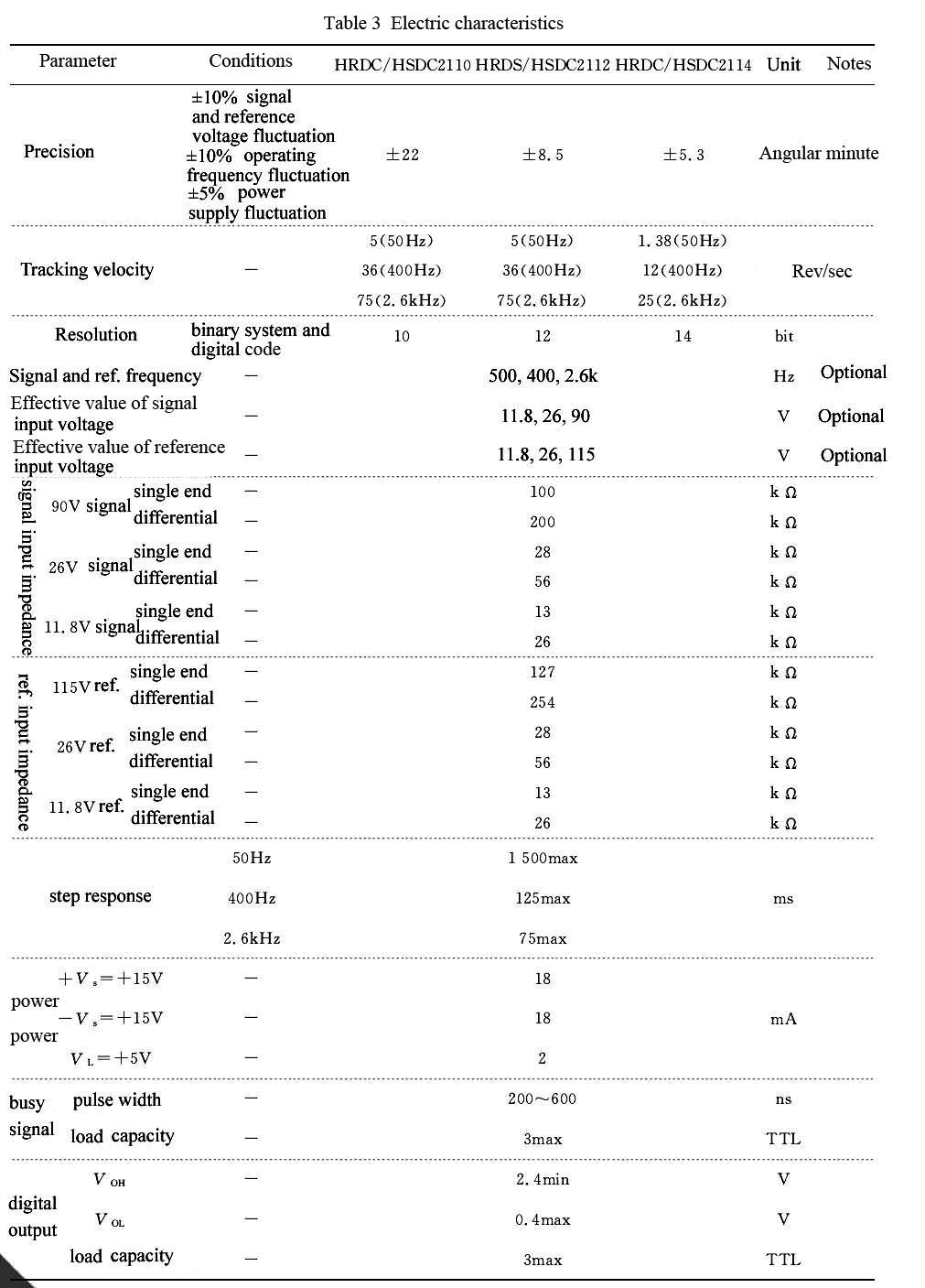

Tabla 2 Condiciones nominales y condiciones de funcionamiento recomendadas | |

máximo absoluto valor nominal | |

Tensión de alimentación Vs: ± 17,5V |

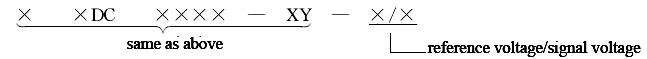

| Valor efectivo del voltaje de referencia VRef: 11.8V, 26V, 115V Valor efectivo de la tensión de referencia V1*: 11,8 V, 26 V, 90 V |  Frecuencia de referencia f*: 50 Hz, 400 Hz, 2,6 kHz |

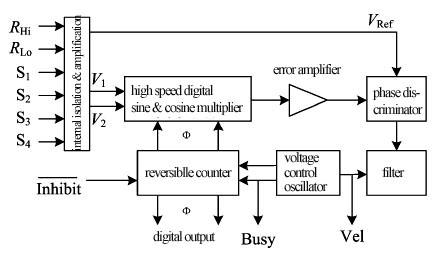

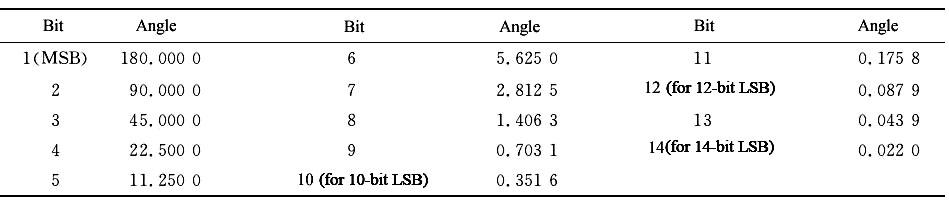

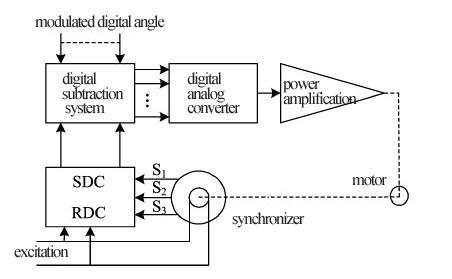

Donde, θ es el ángulo de entrada analógica La señal ortogonal se multiplica por el ángulo digital binario φ en el La señal ortogonal se multiplica por el ángulo digital binario φ en el | contador reversible interno en la función seno-coseno multiplicador y |

θ-φ≠0, el oscilador controlado por voltaje emitirá un pulso para cambiar el | datos en el contador reversible, hasta que θ-φ se vuelve cero dentro del |

|  |

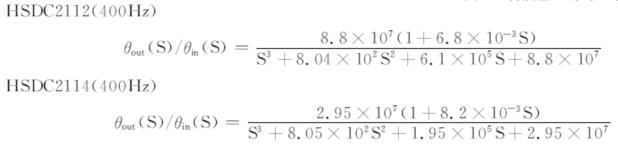

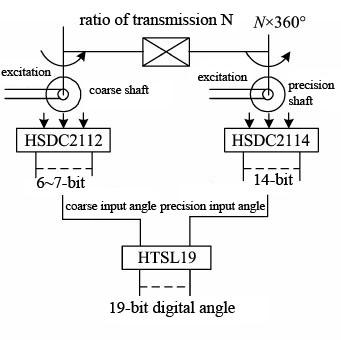

| precisión del convertidor, durante este proceso, el convertidor rastrea la cambio del ángulo de entrada θ todo el tiempo. Para conocer el principio de funcionamiento, consulte la Fig. | 2. Función de transferencia: los siguientes son parámetros para la función de transferencia de HSDC2112 y HSDC2114 (400 Hz), para otros modelos, póngase en contacto con el fabricante directamente. Fig.2 Diagrama de bloques para el principio de funcionamiento del convertidor |

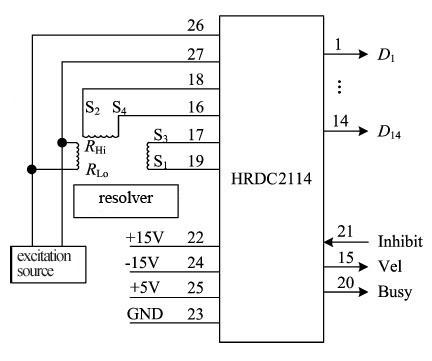

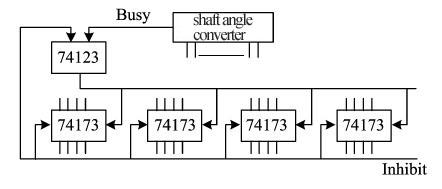

Hay dos métodos para leer los datos válidos del convertidor de la siguiente manera: | Método de inhibición (lectura síncrona): | Establezca Inhibit en la lógica "0", en este momento, el convertidor dejará de rastrear. Esperar | 1 μs hasta que los datos de salida sean estables, lea los datos, los datos leídos son los | válido en este momento (se ha retrasado 1 μs). Establecido en la lógica "1", en este momento, el convertidor comenzará a rastrear nuevamente para prepararse para leer los siguientes datos válidos. | Método ocupado (lectura asíncrona): Inhibir |

1 | D1 | En el modo de lectura asincrónica, | 15 | está configurado en "1" lógico o vacante, si el lazo interno está siempre en modo estable | El estado o si los datos de salida son válidos se determinará a través del |

2 | D2 | estado de señal de ocupado Ocupado. Cuando la señal de ocupado está en un nivel alto, | 16 | S4 | indica que los datos se están convirtiendo, y los datos en este momento son |

3 | D3 | inestable e inválido; cuando la señal de Ocupado está en un nivel bajo, indica el | 17 | S3 | la conversión de datos se ha completado, y los datos en este momento son estables |

4 | D4 | y valido En el modo de lectura asincrónica, la salida Ocupada es un tren de pulsos de | 18 | S2 | Nivel TTL, el ancho entre está relacionado con la velocidad de rotación. Referirse a |

5 | D5 | diagrama de secuencia de tiempo de la transferencia de datos Fig. 3. | 19 | S1 | Fig.3 Secuencia de tiempo de la transferencia de datos |

6 | D6 | (2)Método de atenuación de la señal de entrada | 20 | Si el sincronizador o resolver que usó el usuario no es estándar, para | hacer que el voltaje de la señal de entrada y el voltaje de excitación de entrada coincidan con el |

7 | D7 | valores nominales del convertidor, el usuario puede adoptar el método de | 21 |

| resistencia de atenuación externa conectada en serie, es decir, por cada 1V |

8 | D8 | superior al valor nominal, conecte una resistencia de 1,1 kΩ en serie en el | 22 | terminal de entrada correspondiente. Al usar el convertidor, la serie | la resistencia en cada terminal debe seleccionarse y suministrarse con precisión, |

9 | D9 | y material de resistencia del mismo lote se adoptará para asegurar | 23 | la precisión de conversión del convertidor dentro de la amplia temperatura | rango, por cada 0.1% el error de coincidencia de la resistencia en serie será |

10 | generar un error de conversión de 1,7 minutos angulares. | El fabricante recomienda que es preferible avisar | 24 | el fabricante para personalizar el sincro o resolver no estándar como | según los parámetros requeridos cuando el usuario los utiliza. |

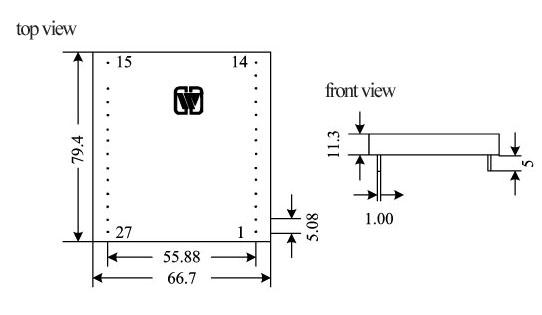

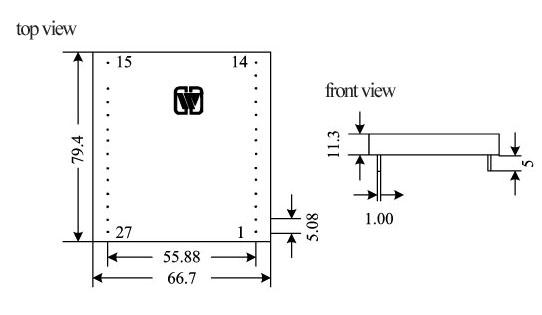

11 | 6 Curva de MTBF (Fig. 4) de convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC211) | 7 Designación de clavijas (Fig. 5, Tabla 4) de convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC211) | 25 | Fig. 4 Curva de temperatura MTBF | (Nota: según GJB/Z299B-98, buen estado del terreno previsto) |

12 | Notas: | ① la estructura anterior es adecuada para HRDC2114 | 26 | ② para SDC, sin pin S4 | ③ para dispositivo de 12 bits, sin pin 13 y 14, para dispositivo de 10 bits, sin pin 11, 12, 13 y 14. |

13 | Fig.5 Designación de clavijas (vista superior) | Tabla 4 Designación de pines | 27 | Clavo | Símbolo |

14 | Función | Clavo |

| Entrada de señal Salida digital de bit 6 Ocupado Entrada de señal ocupada |  |

| Salida digital de bit 7 |

| -15V |  -Fuente de alimentación de 15V |

D11 |

|  |

| +5V Fuente de alimentación | D12 |

X

X