| Conversión de aislamiento diferencial interno |  |

| resolución de 16 bits | |

| Precisión: 2 minutos angulares | |

| Salida de pestillo de tres estados | |

| Alta velocidad de seguimiento continuo | |

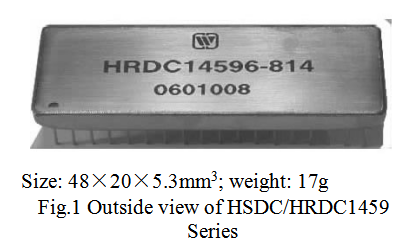

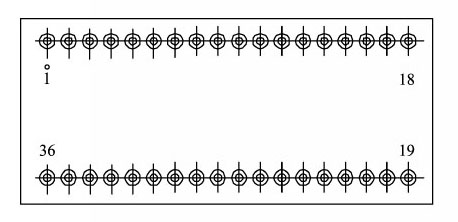

| Paquete DDIP sellado con metal resistente a la niebla salina de 36 hilos | |

| Compatible pin a pin con el modelo SDC14560 de la empresa DDC |

| dispositivo de conversión integrado para el seguimiento continuo diseñado en el | principio del servo modelo II. Los productos de esta serie están diseñados y |

| fabricado por el proceso MCM, los elementos centrales adoptan un chip especial | |

| desarrollado independientemente por nuestro instituto. La disposición de los pines es | |

| compatible con los productos de la serie SDC14560 de la empresa estadounidense DDC, 16 bits | |

| Salida de pestillo de datos de código binario natural paralelo, DIP de 36 líneas totalmente | |

| Paquete de metal sellado, tiene las ventajas de alta precisión, pequeño | |

| volumen, bajo consumo de energía, peso ligero y alta fiabilidad, etc., | y puede ser ampliamente utilizado en importantes armas estratégicas y tácticas como |

| avión, buque de guerra, cañón, misil, radar, tanque, etc. | |

| 4. Rendimiento eléctrico (Tabla 1, Tabla 2) | |

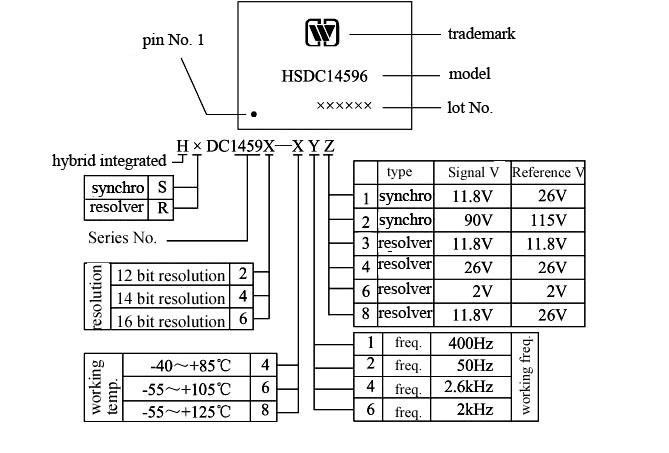

| Convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC1459) | |

| Tabla 1 Condiciones nominales y condiciones de funcionamiento recomendadas | |

| Máx. absoluta valor nominal |

| Tensión de señal V1: valor nominal ±20 % | Tensión de referencia VRef: valor nominal ±20 % | Frecuencia de funcionamiento f: valor nominal ±20 % | |

| Prueba de temperatura de almacenamiento: -65 ~ 150 ℃ | Condiciones de operación recomendadas | ||

| Voltaje de suministro lógico VL: 5±0.5V | Tensión de alimentación Vs: 15± 0,75 V | ||

| Tensión de señal V1: valor nominal ±10 % | Tensión de referencia VRef: valor nominal ±20 % | Frecuencia de funcionamiento f: valor nominal ±20 % | — |

| Rango de temperatura de funcionamiento (TA): -55 ℃ ~ 125 ℃ | Nota: * indica que se puede personalizar según los requisitos del usuario. | Tabla 2 Características eléctricas | Parámetro |

| Condiciones | — | Serie HSDC14569 | (VSu003d15 V, VLu003d+5 V) |

| Estándar militar (Q/HW20725-2006) | — | 2V | mín. |

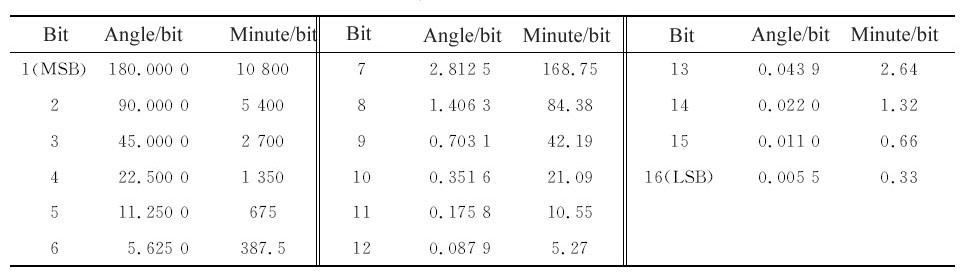

| máx. | — | Resolución | Código digital paralelo del sistema binario |

| 16 bits | — | 2V | Exactitud |

| ± 10 % del voltaje de la señal, voltaje de referencia y rango de fluctuación de la frecuencia de operación | — | -2 minutos angulares | +2 minutos angulares |

| Rango de frecuencia de referencia | — | 50Hz | 2600Hz |

| Rango de voltaje de referencia | — | 115V | Impedancia de entrada de referencia |

4.4kΩ 4.4kΩ | — | 0 | 129,2 kΩ |

Rango de voltaje de la señal Rango de voltaje de la señal | — | 0 | 90V |

Impedancia de entrada de señal Impedancia de entrada de señal | — | 0 | 4.4kΩ |

| 102,2 kΩ | — | Cambio de fase de señal/referencia | —70° |

| +70° | — | Nivel lógico de entrada | Lógica "1" ≥3.3V |

| Lógica “0” ≤0,8 V | — | aporte | 0,8 V |

| aporte | — | 0,8 V | |

| aporte | — | — | 0,8 V |

| Nivel lógico de salida | — | — | Lógica "1" ≥3.3V |

| Lógica “0” ≤0,8 V | — | — | Salida de código de ángulo digital |

| Lógica "1" ≥3.3V | — | — | Lógica “0” ≤0,8 V |

| Conversión de salida de señal de ocupado (CB) | — | 200ns | 600ns |

| Salida de bits de detección de fallas | El "0" lógico indica fallo | — | Capacidad de carga |

| 3TTL | Velocidad de seguimiento | ||

| 2,5 rps | Constante de aceleración | ||

| +10V Actual VSu003d+15V 10mA |  VS u003d—15V |

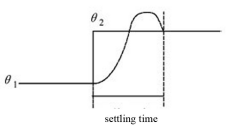

velocidad. El proceso de oscilación del ángulo digital de salida se muestra en

velocidad. El proceso de oscilación del ángulo digital de salida se muestra en 6. Principio de funcionamiento (Fig. 3)

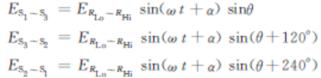

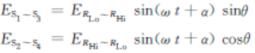

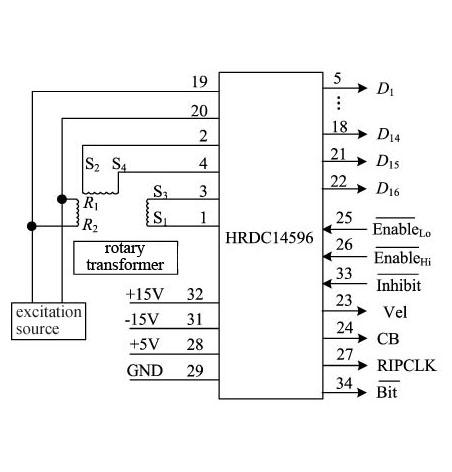

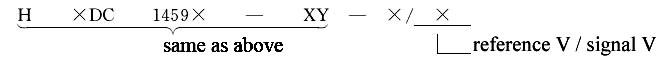

6. Principio de funcionamiento (Fig. 3)| Convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC1459) La señal de entrada de sincronización (o resolución) se convierte en la señal ortogonal a través del aislamiento diferencial interno: | |

Vcosu003dKE0sen (ωt+α) cosθ (cos)ofDonde, θ es el ángulo de entrada analógica. Fig.2 Curva de respuesta al paso | Estas dos señales y el ángulo digital φ del contador reversible internoof se multiplican en el multiplicador de las funciones Seno y Coseno y se error tratado: |

| amplificación, discriminación de fase y filtración de integración, si | θ-φ≠0, el oscilador controlado por voltaje emitirá los pulsos, y el | contador reversible cuenta, hasta que θ-φ se vuelve cero dentro de la precisión de | el convertidor, durante este proceso, la conversión rastrea el cambio de | ángulo de entrada todo el tiempo. | Método de lectura: |

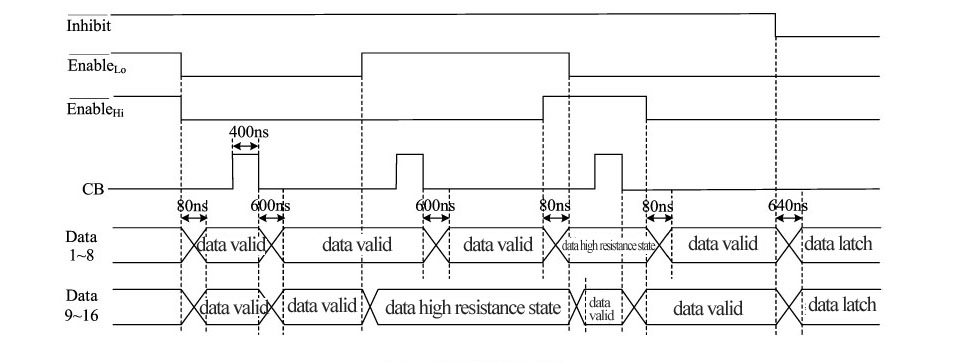

| 1 | S1 | Los siguientes dos métodos están disponibles para la transferencia de datos: | 25 |  | (1) Método de inhibición: |

| 2 | S2 | Después de 640ns de | 26 |  | Lógica baja, los datos de salida son válidos y el convertidor realiza la transferencia de datos a través de |

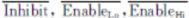

| 3 | S3 | y | 27 | . Después de liberar Inhibir, el sistema generará automáticamente un pulso con un ancho igual al pulso ocupado para la actualización de datos. | (2) Modo busto: |

| 4 | S4 | En el flanco ascendente del pulso Ocupado, cuenta el contador reversible de tres estados; en el flanco descendente del pulso ocupado, genera internamente un pulso de bloqueo con un ancho igual al pulso ocupado para actualizar los datos del bloqueo de tres estados, la secuencia de tiempo de la transferencia de datos se muestra en la Fig. 4, en otras palabras, después de 600 ns de Lógica ocupada baja, la transferencia estable de datos es válida. En el modo de lectura asincrónica, la salida Ocupada es un tren de pulsos de nivel CMOS. El ancho de su nivel alto y bajo depende de la frecuencia de operación y la velocidad de rotación del dispositivo seleccionado. | 28 | VL | Fig.4 Secuencia de tiempo de la transferencia de datos |

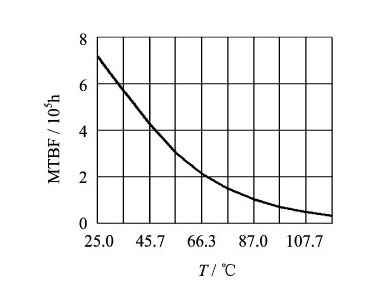

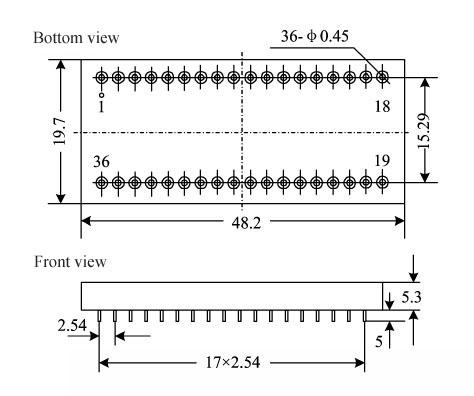

| 7. Curva MTBF (Fig.5) | Convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC1459) | Fig.5 Curva MTBF-temperatura | 29 | 8. Designación de clavijas (Fig. 6, Tabla 3) | Convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC1459) |

| 19 | Fig.6 Designación de pines (vista inferior) | (Nota: según GJB/Z299B-98, buen estado del terreno previsto) | 30 | NC | Tabla 3 Designación de pines |

| 20 | RL | Clavo | 31 | Símbolo | Significado |

| 21 | Clavo | Símbolo | 32 | VS | Significado |

| 22 | Entrada de resolución S1 (o entrada sincronizada S1) | Control digital habilitado de 8 bits inferiores | 33 | Entrada de resolución S2 (o entrada sincronizada S2) | Control digital habilitado de 8 bits superiores |

| 23 | Entrada de resolución S3 (o entrada sincronizada S3) | RIP CLK | 34 | Salida de señal de bit cero | Entrada de resolver S4 (dejar sin conectar) |

| 24 | CB | +5V fuente de alimentación | 18 de mayo | NC | D1-D14 |

| Salida digital 1 (MSB) -14 | TIERRA |

| Tierra | RHola |

| Entrada de señal de referencia de gama alta | Sin conexión |

| RL | Entrada de señal de extremo inferior de referencia |

-VS

-VS -Fuente de alimentación de 15V

-Fuente de alimentación de 15V

D15 Salida digital 15

Salida digital 15 ).

).

+15V Fuente de alimentación

D16

Salida digital 16 (LSB)

Inhibir

Entrada de señal estática

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Entrada de señal de extremo inferior de referenciaofMás bajo | Entrada de señal habilitada de dígitos de 8 bits, este pin es el pin de entrada lógica deofcontrol de puerta de datos, su función es llevar a cabo el control de tres estados |

|  |

| externamente en los datos de salida inferiores de 8 bits del convertidor. El nivel bajo es | válido, los datos de salida de 8 bits inferiores del convertidor ocupan los datos |

estado de resistencia, y el dispositivo no ocupa el bus de datos. Permitiry el tiempo de retardo de liberación es de 600 ns (máx.). | más alto | Entrada de señal habilitada de dígitos de 8 bits, este pin es el pin de entrada lógica de | control de puerta de datos, su función es llevar a cabo el control de tres estados | externamente en los datos de salida de 8 bits más altos del convertidor. Nivel bajo | es válido, los datos de salida de 8 bits más altos del convertidor ocupan elbus de datos; En un nivel alto, el pin de datos de salida de 8 bits más altos está en alto | estado de resistencia, y el dispositivo no ocupa el bus de datos. Permitir | y el tiempo de retardo de liberación es de 600 ns (máx.). | Inhibir estática |

entrada de señal, este pin es el pin de entrada de la lógica de control, su función | es enviar datos externamente al convertidor para realizar opcional | Nicontrol de enganche o derivación. A alto nivel, los datos de salida del | el convertidor emite directamente sin enclavamiento; a bajo nivel, la salida | Los datos del convertidor están bloqueados, los datos no se actualizan, pero elel bucle interno no se interrumpe, y el seguimiento está funcionando todo el | tiempo, Inhibit ha conectado la resistencia pull-up internamente. Después de 600 ns (máx.) de retraso de | Au flanco descendente de la señal estática, los datos se vuelven estables (si el | dispositivo ocupa el bus de datos, es decir, cuándo emite los datos dependesobre el estado de | ySalida de señal CB "Ocupado", esta señal indica si el código binario |

X

X