| Alta precisión |  |

| Talla pequeña | |

| Alta velocidad de seguimiento | |

| Seguimiento ininterrumpido durante la transferencia de datos | |

| Salida de pestillo de tres estados | |

| Bajo consumo de energía |

la señal de salida es un código binario natural paralelo almacenado en búfer a través de | Pestillo de tres estados y compatible con nivel TTL. |

El producto aplica un circuito servo de segundo orden con un tamaño pequeño y ligero. | |

peso, y el usuario puede usarlo muy convenientemente controlando | |

pines de señal | |

Tabla 2 Condiciones nominales y condiciones de funcionamiento recomendadas | máx. valor absoluto de calificación |

Tensión de alimentación +VS: 12,5~17,5 V | |

Tensión de alimentación -VS: -17,5~-12,5 V | |

Voltaje lógico VL: 7V | |

Rango de temperatura de almacenamiento: -40~+100℃ | |

Condiciones de operación recomendadas |

Tensión de referencia (valor efectivo) VRef: valor nominal ±10% | Tensión de señal (valor efectivo) V1*: valor nominal ±10% Frecuencia de referencia f*: valor nominal ±10% | Rango de temperatura de funcionamiento TA: -40~+85 ℃ | Nota: * indica que se puede personalizar según los requisitos del usuario. | |

Tabla 2 Características eléctricas | Parámetro | |||

Condiciones (-40~+85℃) | (A menos que se especifique lo contrario) | 12 | 16 | (serie MSDC/MRDC37) |

Unidad | – | 3 | 36 | mín. |

máx. | Resolución/RES | Rango de 0~360º | – | V |

Poco | Velocidad de seguimiento/St① | – | rps | V |

Alto nivel de salida/VOH | TAu003d25℃ | – | 2.4 | W |

Bajo nivel de salida/VOL | TAu003d25℃ | – | 0.8 | % |

Consumo de energía/DP | – | 2 | TAu003d25℃ | V |

1.3 | – | 2 | 90 | V |

Linealidad de Vel/ERl | – | 30 | TAu003d25℃ | Hz |

1.0 | – | ±3 | Rango de voltaje de referencia | 115 |

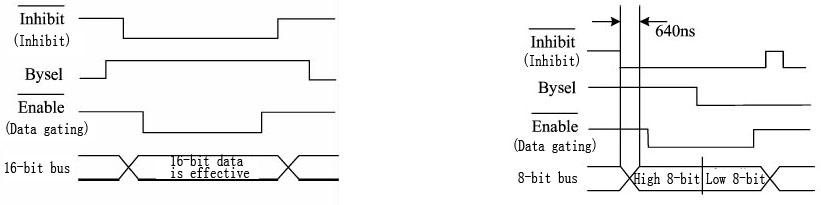

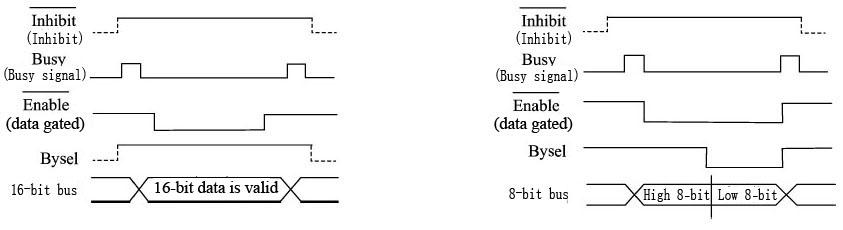

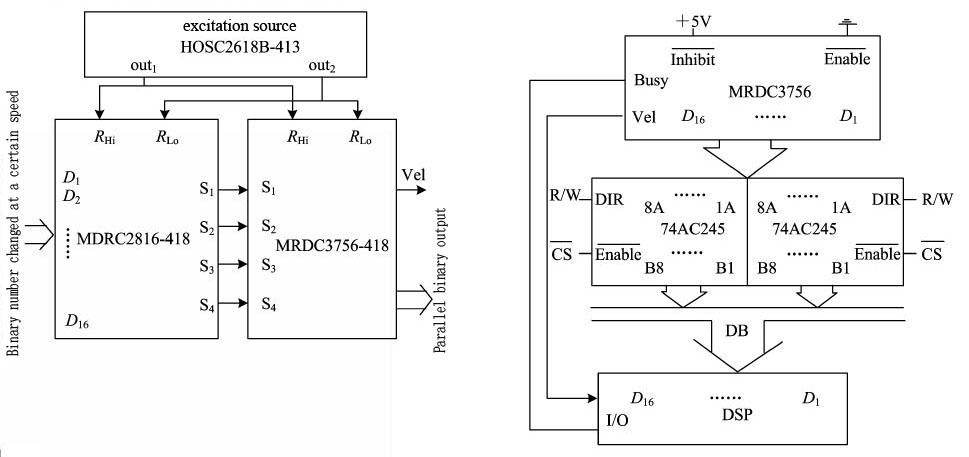

B: el convertidor está conectado al bus de 8 bits, los bits D1 ~ D8 están conectados al bus de datos y el resto está vacío. | Configure la inhibición de lógica 1 a lógica 0 (bloqueo de datos) y espere 1 μs; establezca Habilitar en 0 lógico para permitir que el latch en el convertidor emita datos; colocar | Bysel a la lógica 1, lea directamente los datos altos de 8 bits, establezca Bysel en | 0 lógico, lea los datos en otros bits con relleno automático de cero en | los bits vacantes; configúrelo en la lógica 1 para prepararse para leer los siguientes datos efectivos (Fig. 5). | Inhibir | Fig4 Secuencia de tiempo de transferencia de bus de 16 bits Fig5 Secuencia de tiempo de transferencia de bus de 8 bits | (2) Método ocupado (lectura asíncrona): | En el modo de lectura asíncrono, está configurado Inhibir en 1 lógico o vacío, ya sea que el bucle interno esté siempre en el |

1 | D1 | se determinará el estado estable o si los datos de salida son válidos | 13 | a través del estado de ocupado señal Ocupado. Cuando la señal de ocupado está en alto | nivel, indica que los datos se están convirtiendo, y los datos en este | 25 | el tiempo es inestable e inválido; cuando la señal de Ocupado está en un nivel bajo, | indica que la conversión de datos se ha completado, y los datos en este |

2 | D2 | el tiempo es estable y válido. Una vez que se produce un nivel alto en Ocupado durante la lectura, | 14 | la lectura en este momento no es válida. En el modo de lectura asincrónica, el | La salida ocupada es un tren de pulsos de nivel TTL, su ancho depende de su | 26 | velocidad de rotación, también hay dos métodos de uso del bus, es decir, 8 bits | y 16 bits, la lectura de datos durante la salida de datos efectiva también es |

3 | D3 | controlado por Habilitar, consulte el diagrama de secuencia de tiempo para la transferencia de datos (Fig. 6 y Fig. 7). | 15 | Fig.6 Diagrama de secuencia de tiempo para transferencia de bus de 16 bits Fig.7 Diagrama de secuencia de tiempo para transferencia de bus de 8 bits | Pines de señal de estado: Ocupado, DIR, R, C. | 27 | Cuando cambia la entrada del convertidor, Busy emite un tren de pulsos | del nivel CMOS, su frecuencia está determinada por la rotación más alta |

4 | D4 | velocidad. Cuando Ocupado está en un nivel alto, significa que el servo de segundo orden | 16 | El circuito en el convertidor está funcionando, los datos en el extremo de la salida digital son | cambiando; por el contrario, la computadora puede leer directamente los datos. | 28 | La señal DIR se utiliza para indicar la rotación hacia adelante/hacia atrás. Cuando la salida | |

5 | D5 | el código es conteo ascendente, la salida es de alto nivel; cuando el código de salida es | 17 | NC | cuenta regresiva, la salida es de bajo nivel. | 29 | Salida de señal cero R.C: cuando los datos de salida aumentan de 1 a | todo 0, o los datos de salida disminuyen de todo 0 a todo 1, el |

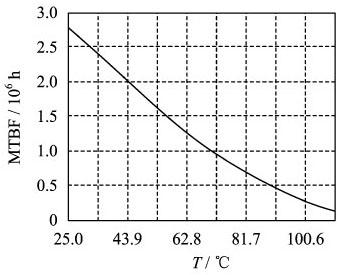

6 | D6 | la salida es un pulso positivo, el ancho del pulso es de 200 μs. | 18 | 5. Curva MTBF de Convertidores Sincro a Digital o Resolver a Convertidores Digitales (serie MSDC/MRDC37)(Fig. 7) | Fig. 8 Curva de temperatura MTBF | 30 | (Nota: según GJB/Z299B-98, se prevé buen estado del terreno) | |

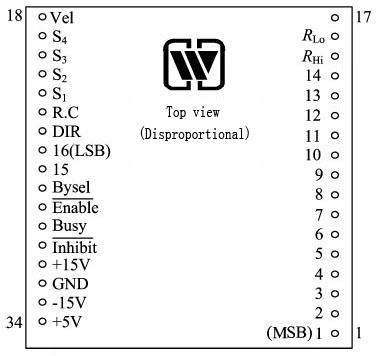

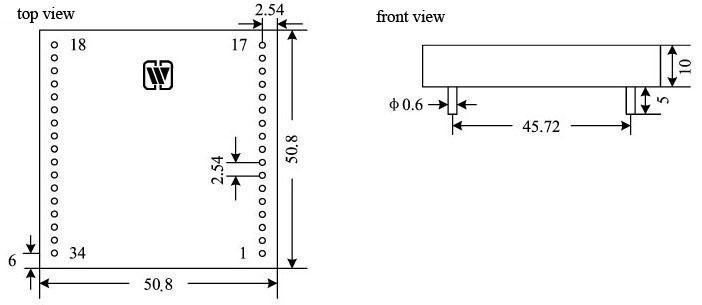

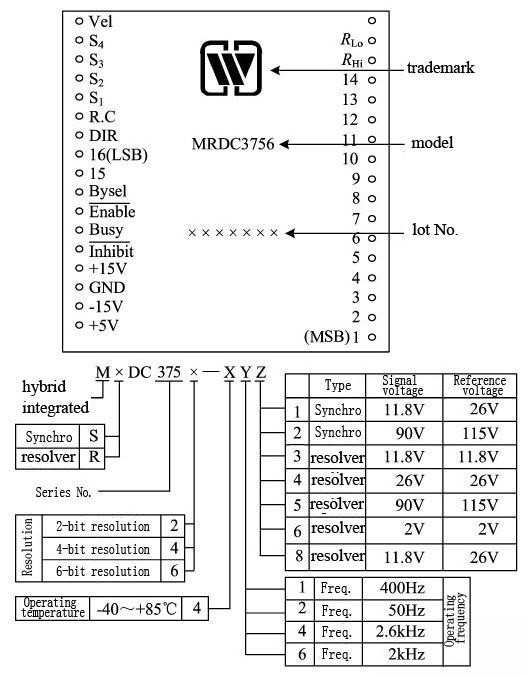

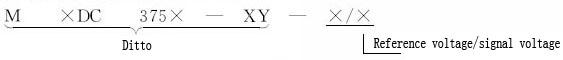

7 | D7 | 6. Designación de clavijas de convertidores sincronizados a digitales o convertidores de resolución a digitales (serie MSDC/MRDC37) (Fig. 9, Tabla 3) | 19 | S4 | Fig.9 Designación de pines (vista superior) | 31 | Tabla 3 Designación de pines | Clavo |

8 | D8 | Símbolo | 20 | S3 | Significado | 32 | Clavo | Símbolo |

9 | D9 | Significado | 21 | S2 | Clavo | 33 | Símbolo | Significado |

10 | Salida digital 1 (bit más alto) | D13 | 22 | S1 | Salida digital 13 | 34 | VL | D16 |

11 | Salida digital 16 | Salida digital 2 | 23 | D14 | Salida digital 14 | |||

12 | D15 | Salida digital 15 | 24 | Salida digital 3 | RHola |

Entrada de señal de referencia (extremo bajo) | Habilitar señal | Salida digital 5 | Callejón sin salida | Ocupado | Señal de ocupado |

Salida digital 6 | Vel | 7 | Salida de voltaje de velocidad | 13 | Señal de inhibición |

2 | Salida digital 7 | 8 | Entrada de señal | 14 | +vs |

3 | +15V Fuente de alimentación | 9 | Salida digital 8 | 15 | Entrada de señal |

4 | TIERRA | 10 | Tierra de poder | 16 | Salida digital 9 |

5 | Entrada de señal | 11 | -vs | ||

6 | -Fuente de alimentación de 15V | 12 | D10 |

| |

| Entrada de señal | +5V Fuente de alimentación |

X

X