| Conversión de aislamiento diferencial interno |  |

| Resolución: 16 bits | |

| Salida de pestillo de tres estados | |

| Seguimiento ininterrumpido durante la transferencia de datos | |

| Paquete metálico de 32 hilos |

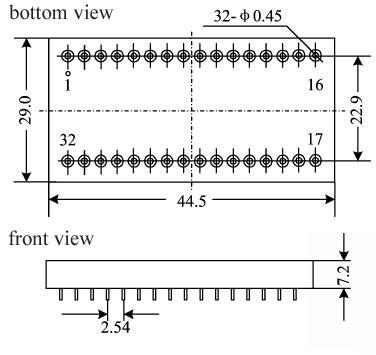

El sincro/resolver de la serie HSDC/HRDC1746 al convertidor digital está diseñado | en el principio del principio de seguimiento servo tipo II y adopta | |||||

entrada de aislamiento diferencial, la salida de datos adopta un pestillo de tres estados | Modo, es adecuado para la conversión de señal analógica/señal digital de | Sincro de tres hilos y resolver de cuatro hilos. Con velocidad de conversión rápida | y un rendimiento estable y confiable, este dispositivo se puede aplicar ampliamente en medición de ángulos y sistema de control automático. | Este producto está hecho por el proceso de integración híbrida de película gruesa y es | ||

Paquete metálico DIP de 32 hilos totalmente sellado. Tanto el diseño como | ||||||

la fabricación del producto satisface los requisitos de GJB2438A-2002 | “Especificación general para circuitos integrados híbridos” y específicas | especificaciones del producto. | ||||

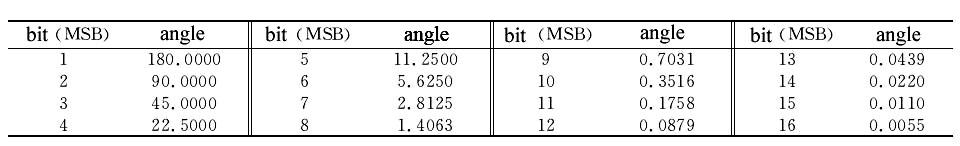

4. Rendimiento eléctrico (Tabla 2, Tabla 3) | Convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC1746) | Tabla 2 Condiciones nominales y condiciones de funcionamiento recomendadas | Tabla 3 Características eléctricas | máximo absoluto valor nominal | ||

Tensión de alimentación Vs: ± 17,25 VCC | Parámetro | -3 | 3 | |||

HSDC/HRDC | Serie 1746 | 16 | ||||

notas | Tensión de alimentación lógica VL: +7V | 50 | Rango de temperatura de almacenamiento: -55 ℃ ~ 150 ℃ | |||

mín. | máx. | 2 | 90 | |||

Condiciones de operación recomendadas | Tensión de alimentación Vs: ±15± 5% | 2 | Precisión/minuto angular | |||

| 2.6k |  |

| Cambio de fase entre señal y excitación: <±10% Tensión de señal (valor efectivo)/V Rango de temperatura de funcionamiento (TA): -40~+105 ℃  | |

| Tensión de referencia (valor efectivo)/V | 115 |

| |

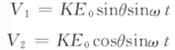

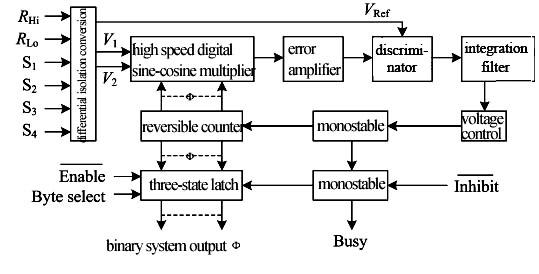

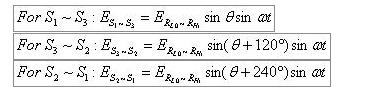

| se obtiene una función de error: |

A través de la amplificación de errores, la discriminación de fase y la filtración de esteof función de error, se obtiene sin(θ-φ), cuando θ-φu003d0 (dentro de la precisión | del convertidor), este error hará que el voltaje controladoofpulso de corrección de salida del oscilador para cambiar el ángulo digital binario φ |

| |

| del contador reversible para hacer que el valor de salida φ sea igual al | entrada θ dentro de la precisión del convertidor, el sistema se estabiliza |

| y puede rastrear el cambio del ángulo de entrada φ. De esta manera, un digital binario | |

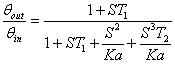

contador reversible (Fig. 2). | Fig. 2 Diagrama de bloques del circuito | (1) Características dinámicas | La función de transferencia del convertidor se muestra en la Fig. 3: | Ganancia de bucle abierto: | Función de circuito cerrado: |

1 | NC | Para el módulo de este modelo Kau003d48000/S2, T1u003d7.1ms, T2u003d1.25ms | 17 | NC | Fig. 3 Transferencia de funciones del convertidor |

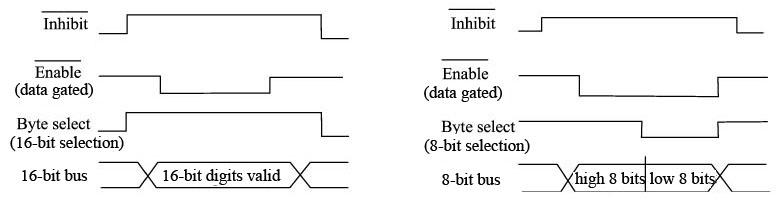

2 | D9 | (2) Métodos de transferencia de datos y secuencia de tiempo | 18 | Control de selección de chip Habilitar | Este pin es el pin de entrada de la lógica de control, su función es dar salida |

3 | datos al convertidor para realizar el control de tres estados. El nivel bajo es | válido, los datos de salida del convertidor ocupan el bus de datos. cuando esta en | 19 | alto nivel, el pin de salida de datos del convertidor está en tres estados, el | dispositivo no ocupa el bus. |

4 | selección de bytes | Este pin es el pin de entrada de control, su función es ejecutar externamente | 20 | control de selección en los datos de salida del convertidor en la transferencia | modo de bus de datos de 8 bits o bus de datos de 16 bits. Cuando la transferencia de bus de datos de 16 bits |

5 | se requiere el modo, mantenga este pin lógico alto, los datos serán | transferido en el bus, la salida de byte alto está en el pin D1 a D8 (D1 es | 21 | bit alto) y el byte bajo está en D9 a D16. Cuando la transferencia de bus de datos de 8 bits | se necesita el modo, los datos se obtienen en el pin D1 a D8 (dispuestos de alta |

6 | a bajo), y los 8 bits altos y los 8 bits bajos se obtienen a través de dos tiempos | secuencias, en otras palabras, cuando Byte select es lógica alta, alta 8 bits | 22 | se emiten y cuando es lógica baja, se emiten 8 bits bajos. | Control de bloqueo de datos (señal de inhibición) Inhibir |

7 | Este pin es el pin de entrada de la lógica de control, su función es dar salida | datos externamente al convertidor para realizar enclavamiento o derivación opcionales | 23 | control. A alto nivel, los datos de salida del convertidor son directamente | salida sin enclavamiento, consulte el diagrama de secuencia de tiempo de los datos |

8 | transferir. En un nivel bajo, los datos de salida del convertidor se bloquean, el | el bucle interno no se interrumpe y el seguimiento sigue funcionando todo el | 24 | D1 | tiempo, pero el contador no genera datos. Cuando se necesita transferir |

9 | datos, el convertidor primero hace una señal de control de inhibición para bloquear los datos de mayor a menor, mantiene la lógica baja durante 640 ns, luego establece la entrada de habilitación en baja (en este momento el dispositivo ocupa el bus de datos), y luego | obtiene datos a través de la selección de bytes, luego cambia todas las lógicas de control a alto | 25 | D2 | para actualizar y bloquear los datos a fin de estar listo para transferir el |

10 | siguientes datos, consulte los diagramas de secuencia de tiempo de la transferencia de datos Fig.4 | y la figura 5. | 26 | D3 | (3)Método de atenuación de la señal de entrada (Fig.4 y Fig.5) |

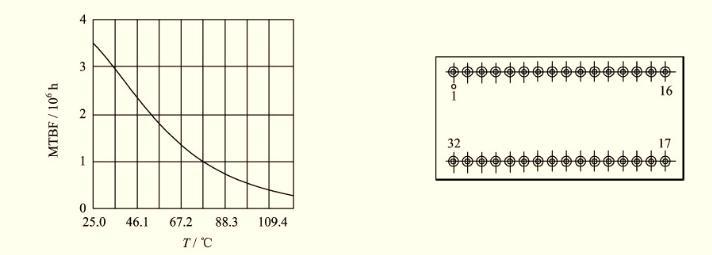

11 | Fig. 4 Secuencia de tiempo de transferencia de bus de 16 bits | Fig5 Secuencia de tiempo de transferencia de bus de 8 bits | 27 | D4 | 6. Curva MTBF (Fig. 6) |

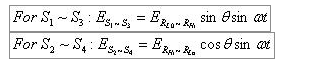

12 | Convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC1746) | 7. Designación de clavijas (Fig. 7, Tabla 4) | 28 | D5 | Convertidores de sincronización a digital o convertidores de resolución a digital (serie HSDC/HRDC1746) |

13 | S3 | Fig.6 Curva MTBF-temperatura | 29 | D6 | Fig.7 Designación de clavijas (vista inferior) |

14 | S2 | (Nota: según GJB/Z299B-98, se prevé buen estado del suelo) | 30 | D7 | Tabla 4 Descripción funcional de los terminales de cables |

15 | S1 | Clavo | 31 | D7 | Símbolo |

16 | NC | Significado | 32 | NC | Clavo |

Tierra | D12 | Salida digital para 12 bits | -VS | -Fuente de alimentación de 15V | D13 | Salida digital para 13 bits | + VS | fuente de alimentación de +15V |

D14 | Salida digital para 14 bits | Ni | Inhibir | Ni | Control de bloqueo de datos | D15 | Salida digital para 15 bits |

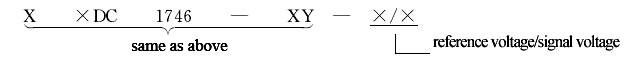

X

X