| Sistema completo de 2 velocidades |  |

| Relaciones de velocidad programables en canal grueso/fino | |

| 1:8, 1:16, 1:32, 1:64 | |

| Salida digital con pestillos de 3 estados | |

| La resolución máxima es de 20 bits. | |

| La precisión máxima es de 5 Arcsec |

| contienen sincro bidireccional grueso/fino a convertidores digitales o resolver a |

|

| convertidores digitales y circuito lógico de corrección de errores requerido por dos |

Las relaciones de velocidad de la combinación gruesa/fina de los productos de la serie HTS20 son | 1:8, 1:16, 1:32, 1:64, la relación de velocidad requerida se puede obtener | programa externo. Es conveniente de usar. Entrada bidireccional gruesa/fina Las señales son señales de sincronización de tres hilos o resolución de cuatro hilos. Convertidor SDC/RDC programable de 2 velocidades serie HTS20 salida natural | códigos binarios paralelos. El máximo es de hasta 20 bits. tienen 3 estados | pestillos | |

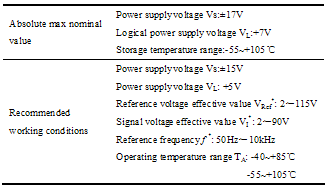

4 ESPECIFICACIONES TÉCNICAS de Convertidores Sincro a Digital o | Resolver a convertidores digitales Serie HTS20 SDC/RDC programable de 2 velocidades | ||||

Convertidores ( Pestaña 2, Pestaña 3 ) | Tabla 2 Condiciones nominales y condiciones de funcionamiento recomendadas * significa que se puede hacer por encargo. Tabla 3 Características eléctricas Características Condiciones | - - - - | 17 18 19 20 | HTS20R/HTS20S | |

Estándar militar empresarial | (Q/HW30925-2006) Unidades Comentarios mínimo máx. | - - - - | 40 20 10 5 | Resolución | |

(opcionalmente controlado por SC1, SC2) relación de velocidad 1:8 1:16 | 1:32 - - - | - 50 2 2 | 36 1:64 poco 90 | Precisión (0°~360°) Hz V V | |

|  |

10k 115 | |

,

, Resolver a convertidores digitales Serie HTS20 SDC/RDC programable de 2 velocidades

Resolver a convertidores digitales Serie HTS20 SDC/RDC programable de 2 velocidades Convertidores (figura 2, figura 3)

Convertidores (figura 2, figura 3) ,

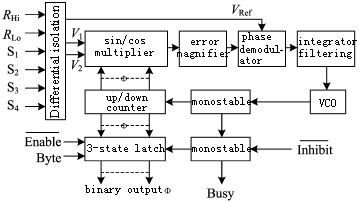

, (1) Convertidor de velocidad única

(1) Convertidor de velocidad única Los principios de funcionamiento del convertidor de una sola velocidad se muestran en la figura 2. Los principios se resumen de la siguiente manera:

Los principios de funcionamiento del convertidor de una sola velocidad se muestran en la figura 2. Los principios se resumen de la siguiente manera: Donde θ es el ángulo de entrada analógica.

Donde θ es el ángulo de entrada analógica. ,

, Las dos señales se multiplican por el ángulo digital φ de subida/bajada interna

Las dos señales se multiplican por el ángulo digital φ de subida/bajada interna .

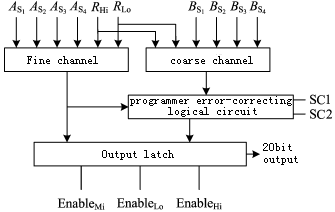

.Los principios de funcionamiento del convertidor de 2 velocidades se muestran en la fig. 3. Él | El funcionamiento del canal grueso y fino del convertidor de 2 velocidades es el |

|  |

| Igual que la velocidad única mencionada anteriormente, pero el convertidor de 2 velocidades consta de dos conjuntos de convertidor de velocidad única y error lógico del programador circuito. El canal grueso cumple con la conversión desde un ángulo lógico de 10 ~ 12 bits | |

ángulo a ángulo digital. ángulos digitales convertidos por canal grueso y | El canal fino se ingresa en la lógica de corrección de errores del programador | circuito respectivamente. Después de procesar y corregir el error, se | genera un dígito binario paralelo de 20 bits, que se ingresa en la salida | Pestillo y amortiguado para dar salida al ángulo digital, cumpliendo todo el | conversión. | |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | Figura 2 Diagrama de bloques funcional Figura 3 Diagrama de bloques funcional de convertidor de una sola velocidad de convertidor de 2 velocidades (3) Método y tiempo de transferencia de datos Las salidas de los convertidores de 2 velocidades de la serie HTS20 alcanzan los 20 bits. A través de y que toman el control de 3 estados del pestillo de salida, el convertidor de 2 velocidades se puede conectar fácilmente al bus de datos. y T1 T2 son todos válidos a bajo nivel. EnableLo controla los 8 bits bajos, EnableMi controla los 8 bits medios, EnableHi controla los bits altos restantes. Los datos de los convertidores de 2 velocidades de la serie HTS20 se leen de la siguiente manera: Colocar a "0" lógico, después de 490 μm, los datos en el latch de 3 estados del convertidor son actualizado Puede leer datos de 8 bits bajos, 8 bits medios y bits altos mediante el control y La figura 4 muestra el tiempo de lectura de datos cuando se conectan un convertidor de 2 velocidades y un bus de datos de 8 bits. Para garantizar una conversión de alta precisión del convertidor de 2 velocidades, preste atención a lo siguiente:

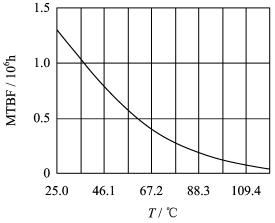

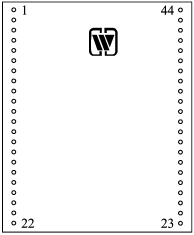

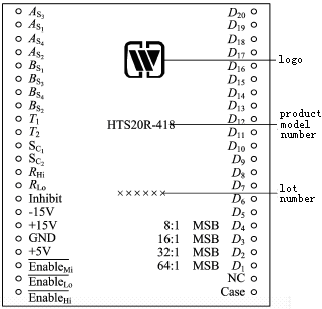

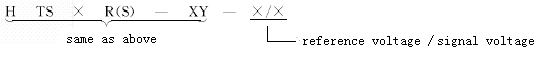

| Las amplitudes de las señales de entrada de los canales gruesos y finos deben garantizarse dentro del valor nominal del 10 %. Las frecuencias de las señales de entrada y las señales de referencia de los canales gruesos y finos deben ser las frecuencias operativas especificadas. Cambio de fase entre la señal de entrada y la señal de referencia de grueso canal y fase entre la señal de entrada y la señal de referencia de multa el canal debe ser inferior a 10°. Las distorsiones de onda de las señales de entrada y las señales de referencia de los canales gruesos y finos deben ser inferiores al 5 %. La variación de la fuente de alimentación de +5V, ±15V debe garantizarse dentro de ±5%. 6 DIAGRAMA MTBF de convertidores sincronizados a digitales o Resolver a convertidores digitales Serie HTS20 SDC/RDC programable de 2 velocidades Convertidores (Fig. 5) CONFIGURACIONES DE 7 PIN de convertidores sincronizados a digitales o Resolver a convertidores digitales Serie HTS20 SDC/RDC programable de 2 velocidades Convertidores (Fig6, Tab4) Figura 5 MTBF vs. temperatura Figura 6 Vista superior del pin out (Nota: Según GJB/Z 299B-98, asumiendo ese suelo está en buenas condiciones) Tabla 4 Descripción del pin Clavo Mnemotécnico Descripción Clavo Mnemotécnico Descripción como3 como1 como4 | 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | como2 NC Bs1 Bs3 Bs4 Bs2 D5 D6 D7 D8 D9 SC1 SC2 RHola RLo Inhibir -15V +15V TIERRA +5V Entrada de canal fino Entrada de canal fino | Entrada de canal fino Entrada de canal fino Entrada de canal grueso Entrada de canal grueso Entrada de canal grueso Entrada de canal grueso Pasador de ajuste para cambio de fase entre señal y referencia Pasador de ajuste para cambio de fase entre señal y referencia Pasador de control de programa para grueso y finas relaciones de velocidad Pasador de control de programa para grueso y finas relaciones de velocidad Pin de entrada para referencia alta Pin de entrada para referencia baja Señal de inhibición -Entrada de 15V entrada +15V tierra entrada +5V habilitar datos de 8 bits intermedios | |

,

, D10

D10 D11

D11 D12

D12 D13

D13 D14

D14

No conectado Salida del ángulo digital combinado más alto | Salida de ángulo digital combinado | Salida de ángulo digital combinado Salida de ángulo digital combinado | Salida de ángulo digital combinado | Salida de ángulo digital combinado Salida de ángulo digital combinado | Salida de ángulo digital combinado |

Salida de ángulo digital combinado | Salida de ángulo digital combinado | 8 | Salida de ángulo digital combinado | 15 | Salida de ángulo digital combinado |

2 | Salida de ángulo digital combinado | 9 | Salida de ángulo digital combinado | 16 | Salida de ángulo digital combinado |

3 | Salida de ángulo digital combinado | 10 | Salida de ángulo digital combinado | 17 | Salida de ángulo digital combinado |

4 | Salida de ángulo digital combinado | 11 | Salida del ángulo digital mínimo combinado | 18 | Nota: |

5 | Pin3,7 de HTS20S no están conectados. | 12 | As1, As2, As3, As4 son una buena entrada de canal. Si el sincronizador está equipado con tres hilos, no se utiliza As4. | 19 | Bs1, Bs2, Bs3, Bs4 son entradas de canal grueso. Si el sincronizador está equipado con tres hilos, no se utiliza Bs4. |

6 | RHi, RLo son entrada de señal de referencia. | 13 | La inhibición es una señal de inhibición que está conectada a una fuente de alimentación de 5 V mediante una resistencia pull-up. Cuando Inhibit es lógico "0", el interior está inhibido. Después de 490 ns, se emiten datos válidos y se pueden leer. Cuando es un "1" lógico, el convertidor restaura el estado de seguimiento, los datos de salida no son válidos. | 20 | Inhibir |

7 | y | 14 | son tres pines de control de estado de salida de datos, que determinaron el estado |

El estuche es un pin de estuche.

D1~D20 son salidas de ángulo digital combinado. D20 es menos significativo

poco. Cuando la relación de velocidad es 1:8, D4 es el bit más significativo. cuando la velocidad | la relación es 1:16, D3 es el bit más significativo. Cuando la relación de velocidad es 1:32, D2 | es el bit más significativo. Cuando la relación de velocidad es 1:64, D1 es más | poco significativo. TABLA DE PESO DE 8 BITS de Convertidores Sincro a Digital o Resolver | a convertidores digitales Serie HTS20 Programables SDC o RDC de 2 velocidades Convertidores (pestaña 5) | Tabla 5 Tabla de peso de bits | Poco | número Peso (grados) | Poco |

número | Peso (grados) Poco | número | Peso (grados) | 1 (MSB) | 180.0000 1.1063 | 0.011(40seg) | 90.0000 |

|

|

| 45.0000 |

X

X